## S.E. (Comp.) (Semester – I) Examination, 2010 ELECTRONIC DEVICES & CIRCUITS (2003 Course)

Time: 3 Hours

Max. Marks: 100

Instructions: 1) Answer any three questions from each Section.

- Answers to the two Sections should be written in separate books.

- 3) Neat diagrams must be drawn wherever necessary.

- 4) Black figures to the right indicate full marks.

- 5) Use of electronic pocket calculator is allowed.

- 6) Assume suitable data, if necessary.

## SECTION - I

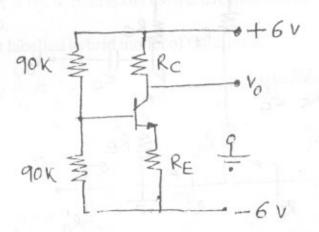

- 1. A) The circuit in fig. 1 uses a silicon transistor with current gain ( $\beta$ ) 200 &  $V_{CEQ} = 3V$ . For the output voltage ( $V_o$ ) to be zero

- i) Determine the value of collector resistance and emitter resistance.

8

ii) With reference to the values in part (1) above, find the new value of  $V_0$  if  $\beta$  is 100.

Fig. 1

B) Explain Thermal Runaway.

- 2. A) Calculate stability factor for a transistor circuit to be thermally stable if the specifications are as under

- Transistor used is NPN and is operated in self bias arrangement

- The component values are  $R_C = 1k$  and  $R_E = 0.1 K$

- The parameter values are  $I_{CO} = 1.2 \text{ nA}$ ,  $\theta = 10 \times 10^8 \text{ °C/W}$ ,  $V_{CEO} = 5.5 \text{ V}$

- The power supply used is +10 volts.

8

- B) Explain with necessary illustrations, what happens when

- i) Operating point is located closer to saturation region

- ii) Operating point is located closer to cutoff region.

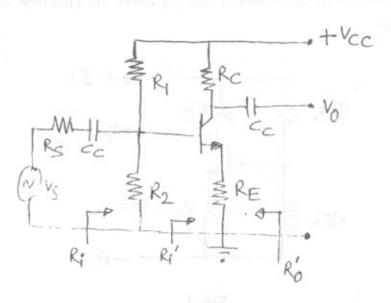

- 3. A) For the circuit in fig. 2

- i) Draw the small signal hybrid model.

2

- ii) Derive in terms of h parameter and circuit component the equations for a) current gain A<sub>1</sub> and A<sub>1S</sub> b) Voltage gain A<sub>2</sub> and A<sub>VS</sub> c) Input impedance

- R<sub>i</sub>' and R<sub>i</sub> d) output impedance R<sub>O</sub> and R'<sub>o</sub>.

10

B) Justify "CE is the only transistor configuration to produce phase shift between input and output signal".

Fig. 2

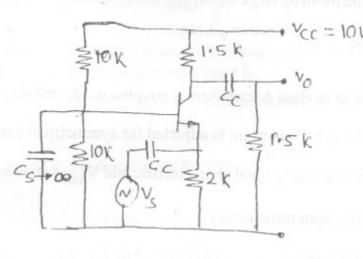

- 4. A) For the circuit in fig. (3), the transistor h parameters are hie = 1k, hfe = 50 and negligible hre and hoe, determine the following

- $i) A_v = \frac{V_0}{V_s}$

- ii)  $A_1 = \frac{i_0}{i_0}$

- iii) R<sub>i</sub>

- iv) R'<sub>0</sub>

10

Fig. 3

B) Draw the circuit diagram and explain importance of

6

- i) Bootstrap emitter follower circuit

- ii) Bootstrap darlington pair

- 5. A) For the circuit in fig. 4, transistors used are identical with hie = 2k, hfe = 100, hre = hoe = 0,

- i) Draw neat labelled hybrid model of the circuit.

2

ii) Determine  $\frac{V_o}{V_s} \& \frac{i_o}{i_s}$ .

8

|    | B) | Explain harmonic and cross over distortion of a power amplifier with necessary           |   |

|----|----|------------------------------------------------------------------------------------------|---|

|    |    | illustrations.                                                                           | 6 |

|    | C) | Explain what you mean by large signal and small signal.                                  | 2 |

|    |    | OR                                                                                       |   |

| 6. | A) | A power transistor in class A transformer coupled mode delivers 5W Power                 |   |

|    | /  | to $5\Omega$ load. The operating point is adjusted for symmetrical current swing         |   |

|    |    | with $V_{cc} = 18$ V. Assuming ideal characteristic and $V_{min} = 0$ , calculate        |   |

|    |    | i) turns ratio of output transformer                                                     |   |

|    |    | ii) peak collector current                                                               |   |

|    |    | iii) Q point coordinates                                                                 |   |

|    |    | iv) collector circuit efficiency and not an analysis of the collector circuit efficiency | 8 |

|    | B) | Draw the circuit diagram of two stage                                                    |   |

|    |    | i) Direct coupled amplifier                                                              |   |

|    |    | ii) R-C coupled amplifier                                                                |   |

|    |    | iii) Single stage transformer coupled amplifier.                                         | 6 |

|    | C) | Explain necessity of multistage amplifier. State the configuration of stages             |   |

|    |    | used in cascade amplifier.                                                               | 2 |

|    | D) | Explain can h parameter be used to analyse large signal amplifier.                       | 2 |

## SECTION - II

| 7  |                          | 공연 집에 가장하다 사람들의 전투에 가장 사람들이 살아지지 않는데 없었다.     | rce follower n channel JFET, consisting                                                           | 2  |

|----|--------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------|----|

|    | 10 10                    | 0 -                                           | nd coupling capacitors C <sub>C</sub> .                                                           | 2  |

|    |                          | ~                                             | ne circuit in part (1) above.                                                                     | 2  |

|    |                          | ation for drain current                       | u                                                                                                 | 2  |

|    | iv) Obtain equ           | ation for voltage gain.                       | A <sub>V</sub> of the circuit.                                                                    | 2  |

|    | v) Can this cir          | rcuit be used to amplif                       | y voltage signal. Justify your answer.                                                            | 2  |

|    | vi) Derive equ           | ation for output resista                      | ance R <sub>o</sub>                                                                               | 2  |

|    | B) Draw the struc        | cture and symbol of n                         | channel EMOSFET. Sketch its transfer                                                              |    |

|    | characteristics          |                                               |                                                                                                   | 4  |

|    | C                        | )R                                            |                                                                                                   |    |

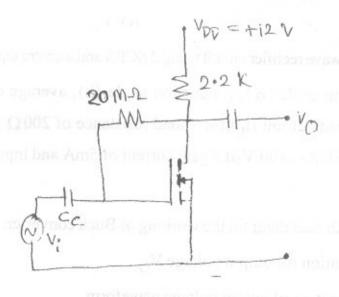

| 8. | A) For the circuit       | in fig. 5, calculate the                      | following                                                                                         |    |

|    | i) g <sub>m</sub>        | ii) r <sub>d</sub>                            |                                                                                                   |    |

|    | iii) A <sub>v</sub>      | iv) R <sub>i</sub>                            | v) R <sub>o</sub>                                                                                 | 10 |

|    | Assume I <sub>D(O)</sub> | $V_{N} = 5.5 \text{ mA}, V_{GS}(C)$           | $(N) = 7.5V$ , $V_T = 3V$ , $Y_{OS} = 50 \mu s$ , $(3 \text{ mA.})$ Use Miller theorem. Calculate |    |

|    | k = 0.25  mA/v           | $V_{GS}^2$ , $V_{GS} = 6.5 \text{ V & I}_D =$ | 3 mA. Use Miller theorem. Calculate                                                               |    |

|    |                          | $r(i/p)$ and $R_{eff}(o/p)$ .                 | O. F. witter CEANT recorders                                                                      | 2  |

Fig. 5

| 9.  | A) | i)   | Draw block diagram of OPAMP.                                                           | 2 |

|-----|----|------|----------------------------------------------------------------------------------------|---|

|     |    | ii)  | Sketch the circuit of level shifter an derive equation for output voltage $V_o$ .      | 4 |

|     |    | iii) | State disadvantage of level shifter and explain how it can be overcome                 |   |

|     |    |      | with the help of necessary circuit.                                                    | 4 |

|     | B) | Di   | raw and explain operation of I to V converter circuit using OPAMP. Derive              |   |

|     |    | eq   | uation for output voltage V <sub>o</sub> . State its application.                      | 6 |

|     |    |      | OR                                                                                     |   |

| 10. | A) | i)   | Draw using OPAMP a circuit to generate a square wave without any input                 |   |

|     |    |      | signal applied to it.                                                                  | 2 |

|     |    | ii)  | Explain its operation with the help of waveforms $V_C \& V_O$ .                        | 4 |

|     |    | iii) | Derive equation for time period T of the square wave.                                  | 4 |

|     | B) | Ex   | cplain OPAMP parameters                                                                |   |

|     |    | i)   | CMRR ii) PSRR                                                                          |   |

|     |    | iii) | Slew rate iv) V <sub>io</sub> .                                                        | 6 |

| 11. | A) | i)   | Draw a full wave rectifier circuit using 2 SCRS and a centre tap transformer.          | 2 |

|     |    | ii)  | Obtain firing angle ( $\alpha$ ), conduction angle ( $\beta$ ), average output voltage |   |

|     |    |      | $(V_o)$ and load current $(i_L)$ for a load resistance of $200\Omega$ if the forward   |   |

|     |    |      | voltage of SCR is 400 V at a gate current of 5mA and input applied is                  |   |

|     |    |      | 600 sin wt.                                                                            | 6 |

|     | B) | i)   | Explain with neat diagram the working of Buck converter.                               | 3 |

|     |    | ii)  | Obtain equation for output voltage V <sub>O</sub>                                      | 3 |

|     |    | iii) | Sketch the nature of output voltage waveform                                           | 2 |

|     | C) | Sk   | etch V-I characteristic of diac                                                        | 2 |

| 12. | (A) | i) State difference between on line and off line UPS.                                     | 2 |

|-----|-----|-------------------------------------------------------------------------------------------|---|

|     |     | ii) Explain operation of on line UPS with neat diagram.                                   | 4 |

|     | B)  | i) Explain operation of SCR using two transistor analogy.                                 | 3 |

|     |     | ii) Derive equation for anode current I <sub>A</sub> .                                    | 3 |

|     | C)  | Define i) Latching current ii) Holding current iii) V <sub>BO</sub> iv) V <sub>BR</sub> . | 6 |

B/II/10/965