Total No. of Questions - [ 08 ]

Total No. of Printed Pages 03

G.R. No.

U218-135(ESE)

## DECEMBER 2018/ENDSEM

S. Y. B. TECH. (E&TC) (SEMESTER - I)

COURSE NAME: DIGITAL ELECTRONINCS

ETUA21175 COURSE CODE:

(PATTERN 2017)

Time: [2 Hours]

[Max. Marks: 50]

- (\*) Instructions to candidates:

- Answer Q.1, Q.2, Q.3, Q.4, Q.5 OR Q.6, Q.7 OR Q.8

- Figures to the right indicate full marks.

- Use of scientific calculator is allowed

- Use suitable data where ever required

- Q.1) a) Use a K-map to simplify each expression to minimum POS form: [6] i)  $Y = (A + \overline{B} + C + \overline{D})(\overline{A} + B + \overline{C} + \overline{D})(\overline{A} + \overline{B} + \overline{C} + \overline{D})$ ii)  $Y = (X + \overline{Y})(W + \overline{Z})(\overline{X} + \overline{Y} + \overline{Z})(W + X + Y + Z)$

- b) Using a K-map, convert the following standard POS expression [6] into a minimum POS expression, a standard SOP expression, and a minimum SOP expression.  $Y = (\overline{A} + \overline{B} + C + D)(A + \overline{B} + \overline{C} + D)(A + B + C + \overline{D})(A + B + \overline{C} + \overline{D})(A + B + \overline{C} + D)$

- Q.2) a) Design a logic circuit to produce a HIGH output only if the [6] input, represented by a 4-bit binary number, is greater than twelve or less than three. Write the truth table and then draw the logic diagram.

- b) Develop a combinational system which has three input and [6] produces output Y. Whenever even number of ones are detected by the system Output Y=1. Write the truth table and draw its logic diagram.

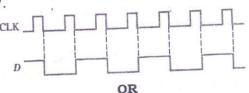

- Q.3) a) Draw the Q output relative to the clock for a D flip-flop with the [6] inputs as shown in fig. Assume positive edge triggering and Q initially LOW.

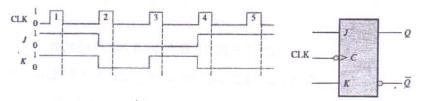

b) The waveform in shown in fig. below is applied to the J, K, and clock inputs as indicated. Determine the Q output, assuming that the flip-flop is initially RESET.

Q.4) a) Design a shift resistor with suitable flip-flops that will follow the [4] sequence 1000, 0100, 0010, 0001, 0000...write its truth table and draw its logic diagram.

OR

- b) Design a synchronous circuit using suitable flip-flop which will [4] follow the sequence 00, 01, 10, 11, 00... write its truth table and draw its logic diagram.

- Q.5) a) A certain IC has two input CMOS NOR gates. Draw the internal [6] diagram of CMOS NOR gate and explain its working for all the possible combination of inputs.

- b) Draw the architecture of CPLD and write its parameters. [4]

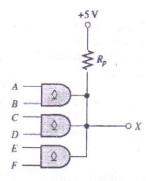

- c) Three open-collector AND gate are connected in a wired AND [4] configuration as shown in figure. Assume that the wired-AND circuit is driving four standard TTL inputs (-1.6 mA each).

- i) Write the logic expression for X.

- ii) Determine the minimum value of  $R_p$  if  $I_{\text{OL}(\text{max})}$  for each gate is 30 mA and  $V_{\text{OL}(\text{max})}$  is 0.4 V

OR

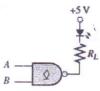

- Q.6) a) A certain IC has four two input TTL NAND gates. Draw the [6] internal structure of TTL NAND gate and explain its working for all the possible combinations of inputs.

- b) A certain IC is of CMOS NOT gates. Draw the internal structure [4] of CMOS inverter gate and explain its working for all possible combinations on input.

- Q.7) a) A long sequences of pulses enters a synchronous sequential [6] circuit which is required to produce an output z=1, whenever the sequence 1111 occurs. Using suitable flip-flop design the non-overlapping system and draw its logic diagram.

- b) With suitable example explain the following terms: [4]

1. State Table 2. State diagram

- c) Write truth table, excitation table for SR flip-flop and draw its state diagram

## OR

- Q.8) a) A long sequences of pulses enters a synchronous sequential circuit which is required to produce an output z=1, whenever the sequence 1010 occurs.

- b) Write truth table, excitation table for JK flip-flop and draw its state diagram

- c) Design a sequence detector which will produce output z=1, [4] whenever the sequence 110 occurs. Using suitable flip-flop design the non-overlapping system and draw its logic diagram.