Marking Scheme

Total No. of Questions - [04]

| G.R. No. |  |

|----------|--|

|          |  |

Total No. of Printed Pages - [03]

U218-145 (TL)

## OCTOBER 2018/ IN-SEM (T1)

S. Y. B. TECH. (INFORMATION TECHNOLOGY) (SEMESTER - I)

**COURSE NAME:**

DIGITAL ELECTRONICS AND LOGIC DESIGN

COURSE CODE:

ITUA21175

**(PATTERN 2017)**

Time: [1 Hour]

[Max. Marks: 30]

- (\*) Instructions to candidates:

- 1) Answer Q.1 OR Q.2 and Q.3 OR Q.4.

- 2) Figures to the right indicate full marks.

- 3) Use of scientific calculator is allowed

- 4) Use suitable data where ever required

- Q.1) a) Convert the following numbers:

- i. (2598.675) 10 = ( ) 16

- ii.  $(110101.101010)_2 = ()_8$

- iii.  $(A72E)_{16} = ()_{8}$

[6 marks]

Marking Scheme: Step-by-step conversion

[2 marks

each

- b) Construct Hamming Code for the following 8-bits word. Use Even Parity.

- i. 10101010

- ii. 00000000

- iii.11111111

[6 marks]

**Marking Scheme:** Hamming code format, show parity bit position, Step-by-step conversion [2 marks each]

c) Define Boolean algebra & Boolean Expression. Explain any 4 basic properties of Boolean algebra? [4 marks]

*Marking Scheme:* Definition Boolean algebra & Boolean Expression [2 marks], any 4 basic properties of Boolean algebra [2 marks].

OR

- Q.2) a) Explain in short with respect to radix, symbols used, weight assigned to position, example, and applications of the following:

- i) Binary Number System

- ii) Hexadecimal Number System

- iii) Octal Number System

[6 marks]

Marking Scheme: Explanation wrt radix, symbols used, weight assigned to position, example, and applications. [2 marks each]

- b) Perform following arithmetic using 2's Complement:

- i) (7) 10 (11) 10

ii) (-7) 10 - (11) 10

iii) (-7) 10 + (11) 10

[6 marks]

Marking Scheme: Step-by-step solution to the above arithmetic and correct answer. [2 marks each]

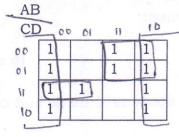

c) Minimize the 4-variable logic function using K-map technique. f(A,B,C,D) = ABC'D + A'BCD + A'B'C' + A'B'D' + AC' + B' [4 marks]

Marking Scheme: 4 variable K-map, grouping 1's, and minimized expression.

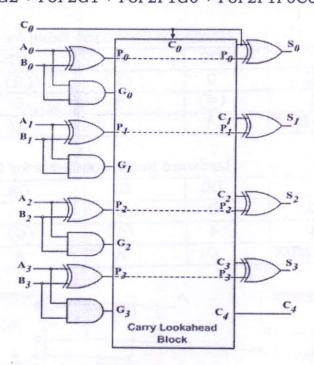

Q.3) a) Explain Adder with Look-Ahead carry. Consider 4-bit adder and formulate Boolean expressions for the carry (C<sub>0</sub>, C<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub>). [6 marks]

*Marking Scheme:* Explanation, Diagram, Boolean Expressions (C<sub>0</sub>, C<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub>).

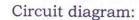

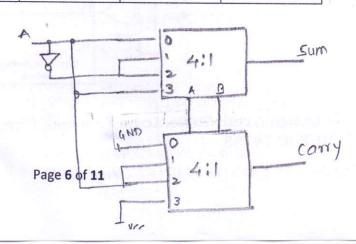

b) Design (Truth Table, Logic Function, Circuit Diagram) Full Adder using MUX IC 74153. [4 marks]

*Marking Scheme:* Truth Table, Logic Function, Circuit Diagram using MUX IC 74153.

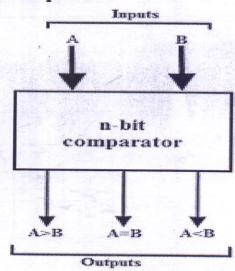

c) Define Digital Comparators. Draw and discuss n-bit comparator. [4 marks]

Marking Scheme: Definition, Diagram, Working, and Example.

#### OR

Q.4) a) Design (Truth Table, K-map, Boolean expressions, Circuit Diagram) and draw the 4-bit Code Converter circuit for converting Excess-3 Code to BCD Code.

[6 marks]

Marking Scheme: Truth Table, K-map, Boolean expressions, Circuit Diagram.

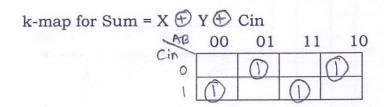

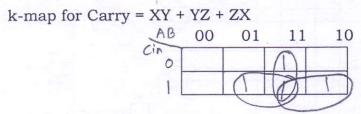

b) Design a Full Adder circuit using logic gates. Show Truth Table, K-map simplification and Circuit diagram. [4 marks]

Marking Scheme: Truth Table, K-map simplification and Circuit diagram.

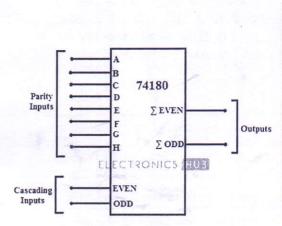

c) Discuss the 8-bit Parity generator/checker circuit IC 74180. [4 marks]

Marking Scheme: 8-bit Parity generator/checker circuit IC 74180 diagram, working, Function table, example.

| G.R. No. |  | hin-t | relate |

|----------|--|-------|--------|

|          |  |       |        |

## OCTOBER 2018/ IN-SEM (T1)

S. Y. B. TECH. (Information Technology) (SEMESTER - I)

COURSE NAME:

Digital Electronics and Logic Design

COURSE CODE:

ITUA21175

## **(PATTERN 2017)**

Time: [1 Hour]

[Max. Marks: 30]

# (\*) Instructions to candidates:

- Answer Q.1 OR Q.2 and Q.3 OR Q.4.

- Figures to the right indicate full marks.

- Use of scientific calculator is allowed

- Use suitable data where ever required

- Q.1) a) Convert (step-by-step conversion) the following numbers:

iii.

$$(A72E)_{16} = ()_8$$

[6 marks]

Marking Scheme: Step-by-step conversion

[2 marks each]

## Integer part

| Divis | Dividend | Remain   |

|-------|----------|----------|

| 16    | 2598     | MARK THE |

| 16    | 162      | 6        |

| 16    | 10       | 2        |

| 16    | 10       | A        |

Fractional part:

Product

Integer part

$$0.675 \times 16 = 0.8 \times 1$$

10.8 12.8 10 (A) 12 (C)

- b) Construct Hamming Code for the following 8-bits word. Use Even Parity.

- i. 10101010

- ii. 00000000

iii.11111111

[6 marks]

Marking Scheme: Hamming code format, show parity bit position, Step-by-step conversion [2 marks each]

|                | So | lution | <b>1:</b> i) 1 | 1110 | 01001 | 010 | ii) | 0000 | 00000 | 00000 | )   | iii) | 111 | 01110 | )1111 |     |                                         |

|----------------|----|--------|----------------|------|-------|-----|-----|------|-------|-------|-----|------|-----|-------|-------|-----|-----------------------------------------|

| Bit position - | 1  | 2      | 3              | 4    | 5     | 6   | 7   | 8    | 9     | 10    | 111 | 12   | 13  | 14    | 15    | 16  | 17                                      |

| Encoded data + | Pi | P2     | di             | Pay  | d2    | Pd3 | d4  | Pg   | ds    | de    | d7  | de   | dq  | dio   | dii   | P16 | d12                                     |

| 1)             | 1  | 1      | 1              | 1    | D     | 1   | D   | 0    | 01    | D     | 01  | 0    | •   | 0     | #     |     | 0                                       |

| (1)            | 0  | 0      | 0              | 0    | 0     | 0   | 0   | 0    | 0     | 0     | 0   | 0    |     |       | 1 10  |     |                                         |

| (V)            | 1  | 1      | 1              | 0    | 1     | 1   | 1   | 0    | 1     | 1     | 1   | 1    |     |       |       |     | *************************************** |

$$P_1 = d_1, d_2, d_4, d_5, d_7, d_9, d_{11}, d_{12}, d_{14}$$

$P_8 = d_5, 6, 7, 8, 9, 10, 11$

$P_2 = d_1, d_3, d_4, d_6, d_7, d_{10}, d_{11}, d_{13}, d_{14}$

$P_6 = d_{12}, d_3, d_4, d_8, d_9, d_{10}, d_{11}, d_{15}$

c) Define Boolean algebra & Boolean Expression. Explain any 4 basic properties of Boolean algebra? [4 marks]

*Marking Scheme:* Definition Boolean algebra & Boolean Expression [2 marks], any 4 basic properties of Boolean algebra [2 marks].

**Solution:** i) A system of algebra that operates on Boolean variables. The binary nature of Boolean algebra makes it useful for analysis, simplification and design of logic circuits. The basic properties of Boolean algebra are commutative property, associative property and distributive property.

**Commutative**: The commutative property says that binary operations AND and OR may be applied left to right or right to left. (A AND B is the same as B AND A; A OR B is the same as B OR A.)

**Associative**: The associative property says that given three Boolean variables, they may be ANDed or ORed right to left or left to right. ((A AND B) AND C is the same as A AND (B AND C); (A OR B) OR C is the same as A OR (B OR C).)

**Distributive**: The distributive property says that given three Boolean variables, the first AND the result of the second OR the third is the same as the first AND the second OR the first AND the third. (A AND (B OR C), = (A AND B) OR (A AND C). Also, the first OR the result of second AND the third is the same as the first OR the second AND the result of the first OR the third. (A OR (B AND C) = (A OR B) AND (A OR C).)

**Identity**: The identity property says that any value A AND the OR identity always returns A and that any value A OR the AND identity always returns A. (A AND 1 = A; A OR 0 = A.)

**Complement:** The complement property says that any value AND the compliment of that value equals the OR identity and that any value OR the compliment of that value equals the OR identity. (A AND (A') = 0; A OR (A') = 1.)

OR

Q.2) a) Explain in short with respect to radix, symbols used, weight assigned to position, example, and applications of the following:

i) Binary Number System

ii) Hexadecimal Number System

iii) Octal Number System

[6 marks]

Marking Scheme: Explanation w.r.t. radix, symbols used, weight assigned to position, example, and applications. [2 marks each]

| Number<br>System | Base<br>Radix | Symbols used                        | Weigh<br>assign<br>positi | ied              | Example |

|------------------|---------------|-------------------------------------|---------------------------|------------------|---------|

| Binary           | 2             | 0,1                                 | 2 <sup>i</sup>            | 2-f              | 1011.11 |

| Octal            | 8             | 0,1,2,3,4,5,6,7                     | 8i                        | 8-f              | 3567.25 |

| Decimal          | 10            | 0,1,2,3,4,5,6,7,8,9                 | 10i                       | 10-f             | 3974.98 |

| Hexadecimal      | 16            | 0,1,2,3,4,5,6,7,8,9,A,B,C,<br>D,E,F | 16 <sup>i</sup>           | 16 <sup>-f</sup> | 3FA9.56 |

b) Perform following arithmetic using 2's Complement:

[6 marks]

*Marking Scheme:* Step-by-step solution to the above arithmetic and correct answer.

Solution:

[2 marks each]

i)

$$(7) = 0111$$

$$(11) = 1011$$

2's compliment of (11) = 0101

0111 + 0101 = 1100; no carry generated, so the answer is -ve and in 2's comp. form.

ii) (-7) = 0111 (-11) = 1011 2's compliment of (-7) = 1001 2's compliment of (-11) = 0101

1001 + 0101 = 1110; sign bit is not same as operands, so there's a problem of overflow.

iii) (-7) = 0111 (11) = 10112's compliment of (-7) = 1001= 1001 + 1011 = 10100; discard the carry

c) Minimize the 4-variable logic function using K-map technique. f(A,B,C,D) = ABC'D + A'BCD + A'B'C' + A'B'D' + AC' + B' [4 marks]

Marking Scheme: 4 variable K-map, grouping 1's, and minimized expression.

#### Solution:

- 1) Enter 1 in the cell with A=1, B=1, C=0, D=1 corresponding to the minterm ABC'D.

- 2) Enter 1 in the cell with A=0, B=1, C=1, D=1 corresponding to the minterm A'BCD.

- 3) Enter 1 in the two cell with A=0, B=0, C=0 corresponding to the minterm A'B'C'.

- 4) Enter 1 in the two cell with A=0, B=0, D=0 corresponding to the minterm A'B'D'.

- 5) Enter 1 in the four cell with A=1, C=0 corresponding to the minterm AC'.

- 6) Enter 1 in the eight cell with B=0 corresponding to the minterm B'.

Y = B' + AC' + A'CD

Q.3) a) Explain Adder with Look-Ahead carry. Consider 4-bit adder and formulate Boolean expressions for the carry (C<sub>0</sub>, C<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub>). [6 marks]

*Marking Scheme:* Explanation, Diagram, Boolean Expressions (C<sub>0</sub>, C<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub>).

- > Solution: In this circuit, the 2 internal signals Pi and Gi are given by:

- ▶ Pi = Ai ⊕Bi .....(1)

- Gi = Ai . Bi .....(2)

- The output sum and carry can be defined as:

- ▶ Si = Pi ⊕ Ci .....(3)

- Ci +1 = Gi + Pi.Ci .....(4)

- ▶ Gi is known as the carry Generate signal since a carry (Ci+1) is generated whenever Gi=1, regardless of the input carry (Ci).

- ▶ Pi is known as the carry propagate signal since whenever Pi =1, the input carry is propagated to the output carry, i.e., Ci+1 = Ci (note that whenever Pi =1, Gi =0).

- Computing the values of Pi and Gi only depend on the input operand bits (Ai & Bi) as clear from the Figure and equations.

- Thus, these signals settle to their steady-state value after the propagation through their respective gates.

- ▶ The Boolean expression of the carry outputs of various stages can be written as follows:

- C1 = G0 + P0C0

- ► C2 = G1 + P1C1 = G1 + P1 (G0 + P0C0)

- = G1 + P1G0 + P1P0C0

- C3 = G2 + P2C2 = G2 + P2G1 + P2P1G0 + P2P1P0C0

- C4 = G3 + P3C3

- = G3 + P3G2 + P3P2G1 + P3P2P1G0 + P3P2P1P0C0

b) Design (Truth Table, Logic Function, Circuit Diagram) Full Adder using MUX IC 74153. [4 marks]

*Marking Scheme:* Truth Table, Logic Function, Circuit Diagram using MUX IC 74153.

Solution: Truth Table

| Inp | uts |   | S | C  |

|-----|-----|---|---|----|

| A   | В   | С |   |    |

| 0   | 0   | 0 | 0 | 0  |

| 0   | 0   | 1 | 1 | 0  |

| 0   | 1   | 0 | 1 | 0  |

| 0   | 1   | 1 | 0 | 1  |

| 1   | 0   | 0 | 1 | 0  |

| 1.5 | 0   | 1 | 0 | 1  |

|     | 1   | 0 | 0 | .1 |

| 1   | 1   | 1 | 1 | 1  |

Sum =  $\sum$ m (1, 2, 4, 7) Carry =  $\sum$ m (3, 5, 6, 7)

### Hardware Reduction Table for Sum:

|              | D0 | D1  | D3_ | D3  |

|--------------|----|-----|-----|-----|

| A!           | 0  | (1) | (2) | 3   |

| A            | 4) | 5   | 6   | (7) |

| Input to MUX | A  | A!  | A!  | A   |

### Hardware Reduction Table for Carry:

|              |    |     |     | A CONTRACTOR OF THE CONTRACTOR |

|--------------|----|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | D0 | D1  | D3  | D3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A!           | 0  | 1   | 2   | (3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A            | 4  | (5) | (6) | (7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Input to MUX | 0  | A   | A   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

c) Define Digital Comparators. Draw and discuss n-bit comparator. [4 marks]

Marking Scheme: Definition, Diagram, Working, example.

**Solution:** Comparators can be designed for comparing multibit numbers. It receives two n-bit numbers A and B as input and the outputs are A > B, A = B, and A < B. Depending on the magnitude of the two numbers, one of

the

output will be HIGH.

### n-bit comparator:

OR

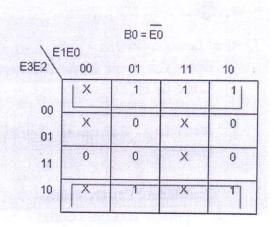

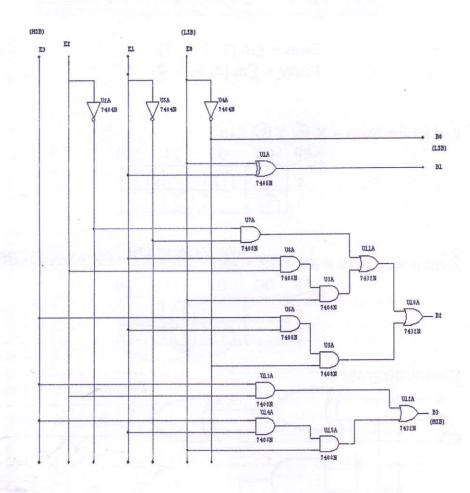

Q.4) a) Design (Truth Table, K-map, Boolean expressions, Circuit Diagram) and draw the 4-bit Code Converter circuit for converting Excess-3Code to BCD Code.[6 marks]

Marking Scheme: Truth Table, K-map, Boolean expressions, Circuit Diagram.

### Solution: Truth Table

| NPUT           | (EXCESS-3      | CODE)          |                | OUTPUT         | (BCD COI       | DE)            |    |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----|

| E <sub>3</sub> | E <sub>2</sub> | E <sub>1</sub> | E <sub>0</sub> | B <sub>3</sub> | B <sub>2</sub> | B <sub>1</sub> | Bo |

| 0              | 0              | 0              | 0              | X              | X              | X              | Х  |

| 0              | 0              | 0              | 1              | X              | X              | X              | X  |

| 0              | 0              | 1              | 0              | X              | X              | X              | X  |

Page 7 of 11

| 9.74 |     |   |   |   |   |   |     |

|------|-----|---|---|---|---|---|-----|

| 0    | . 0 | 1 | 1 | 0 | 0 | 0 | . 0 |

| 0    | 1   | 0 | 0 | 0 | 0 | 0 | 1   |

| 0    | 1   | 0 | 1 | 0 | 0 | 1 | 0   |

| 0    | 1   | 1 | 0 | 0 | 0 | 1 | 1   |

| 0    | 1   | 1 | 1 | 0 | 1 | 0 | 0   |

| 1    | 0   | 0 | 0 | 0 | 1 | 0 | 1   |

| 1    | 0   | 0 | 1 | 0 | 1 | 1 | 0   |

| 1    | 0   | 1 | 0 | 0 | 1 | 1 | 1   |

| 1    | 0   | 1 | 1 | 1 | 0 | 0 | 0   |

| 1    | 1   | 0 | 0 | 1 | 0 | 0 | 1   |

| 1    | 1   | 0 | 1 | Х | Х | X | X   |

| 1    | 1   | 1 | 0 | X | Х | X | X   |

| 1    | 1   | 1 | 1 | Х | X | X | · X |

### K-Map For Reduced Boolean Expressions Of Each Output

| \ E1 |    | 3 = E3E2 + | E3E1E0 |    |

|------|----|------------|--------|----|

| E3E2 | 00 | 01         | 11     | 10 |

| 00   | Х  | 0          |        | 0  |

| 01   | ×  | 0          | X      | 0  |

| 11   | 0  | 0          | X      | 1  |

| 10   | X  | 0          | X      | 0  |

| E3E2 E1 | E0 |    |    |      |

|---------|----|----|----|------|

| E3E2 \  | 00 | 01 | 11 | 10 , |

| 00      | X  | 0  | 0  |      |

| 01      | Х  | 0  | Х  | 1_1_ |

| 11      | 0  | 1  | х  | 0    |

| 10      | X  | 0  | X  | 11   |

|        | B1 = E1E0 +E1E0 |    |    |    |  |  |

|--------|-----------------|----|----|----|--|--|

| 3E2 E1 | E0<br>00        | 01 | 11 | 10 |  |  |

|        | Х               | 0  | 0  | 0  |  |  |

| 00     | X               | 1  | Х  | 1  |  |  |

| 01     | 0               | 0  | Х  | 0  |  |  |

| 10     | X               | 1  | Х  | 1  |  |  |

**Circuit Diagram**

b) Design a Full Adder circuit using logic gates. Show Truth Table, K-map simplification and Circuit diagram. [4 marks]

Marking Scheme: Truth Table, K-map simplification and Circuit diagram.

Solution: Truth Table

| Inj | Inputs |    | Sum | Carry |  |

|-----|--------|----|-----|-------|--|

| Α   | В.,    | С  |     |       |  |

| 0   | 0      | 0  | 0   | 0     |  |

| 0   | 0      | 1  | 1   | 0     |  |

| 0   | 1 2.3  | 0  | 1   | 0     |  |

| 0   | 1      | 1. | 0   | 1     |  |

| 1   | 0      | 0  | 1   | 0     |  |

| 1   | 0      | 1  | 0   | 1     |  |

| 1.  | 1      | 0  | 0   | 1     |  |

Sum =

$$\sum m (1, 2, 4, 7)$$

Carry =  $\sum m (3, 5, 6, 7)$

Circuit diagram:

X

Y

CIN

COUT

c) Discuss the 8-bit Parity generator/checker circuit IC 74180. [4 marks]

*Marking Scheme:* 8-bit Parity generator/checker circuit IC 74180 diagram, working, Function table, example.

#### Solution:

A parity generator is a combinational logic circuit that generates the parity bit in the transmitter. On the other hand, a circuit that checks the parity in the receiver is called parity checker. A combined circuit or devices of parity generators and parity checkers are commonly used in digital systems to detect the single bit errors in the transmitted data word.

The sum of the data bits and parity bits can be even or odd. In even parity, the added parity bit will make the total number of 1s an even amount

whereas in odd parity the added parity bit will make the total number of 1s odd amount.

It is a 9-bit parity generator or checker used to detect errors in high speed data transmission or data retrieval systems. The figure below shows the pin diagram of 74180 IC.

This IC can be used to generate a 9-bit odd or even parity code or it can be used to check for odd or even parity in a 9-bit code (8 data bits and one parity bit).

This IC consists of eight parity inputs from A through H and two cascading inputs. There are two outputs even sum and odd sum. In implementing generator or checker circuits, unused parity bits must be tied to logic zero and the cascading inputs must not be equal.

**FUNCTION TABLE**

| INP                     | OUTPUTS |     |           |          |

|-------------------------|---------|-----|-----------|----------|

| Σ OF H's AT<br>A THRU H | EVEN    | ODD | Σ<br>EVEN | Σ<br>ODD |

| EVEN                    | н       | L   | Н         | L        |

| ODD                     | Н       | L   | L         | Н        |

| EVEN                    | L       | H   | L         | Н        |

| ODD                     | L       | H   | H         | L        |

| ×                       | Н       | Н   | L         | L        |

| ×                       | L       | L   | Н         | Н        |

H = high level, L = low level, X = irrelevant