Marking Schema

Total No. of Questions - [04]

Total No. of Printed Pages - [02]

| G.R. No. |  |  |

|----------|--|--|

|          |  |  |

OCTOBER 2018/ IN-SEM (T2)

U218-145 (TZ)

S. Y. B. TECH. (INFORMATION TECHNOLOGY) (SEMESTER - I)

COURSE NAME:

DIGITAL ELECTRONICS AND LOGIC DESIGN

**COURSE CODE:**

ITUA21175

(PATTERN 2017)

Time: [1 Hour]

[Max. Marks: 30]

- (\*) Instructions to candidates:

- 1) Answer Q.1 OR Q.2 and Q.3 OR Q.4.

- 2) Figures to the right indicate full marks.

- 3) Use of scientific calculator is allowed

- 4) Use suitable data wherever required

- Q.1) a) Explain the operation of a twisted-ring counter and give its [6 marks] state diagram.

Marking scheme: Block diagram with explanation and state [2-marks diagram. each]

b) Design a Sequence Generator using Shift Register IC 74194 to [6 marks] generate the sequence 10110.

Marking scheme: Show number of FFs required, draw state [2-marks table, k-map, logic expression, and circuit diagram. each]

c) Design a divide-by-96 (MOD-96) counter using IC 7490. [4 marks]

OR

Q.2) a) Design the circuit for 3-bit Synchronous Up-Counter.

[6 marks]

*Marking scheme: D*raw state table, k-map, logic expression, and circuit diagram.

b) Convert JK flip-flop to D flip-flop. Show the design.

[6 marks]

*Marking scheme:* Excitation table, k-map, logic expression, and circuit diagram.

c) Design the circuit for 3-bit Asynchronous Down-Counter. Show output waveforms of counter. [4 marks]

Marking scheme: Circuit diagram and waveforms.

Marking scheme: Architecture and explanation.

[2-marks each]

Q.3) a) Explain the basic architecture of FPGA with suitable diagram. [6 marks]

b) Design 4:1 MUX using suitable PAL.

[4 marks]

Marking scheme: Truth table, PAL program table, circuit

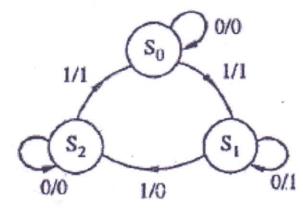

c) Draw an equivalent ASM chart for the state diagram shown below. It has 3 states, inputs x, and outputs z.

[4 marks]

Marking scheme: ASM chart with proper notations.

OR

Q.4) a) Design 3-bit Binary to Gray code converter using suitable PLA. [6 marks]

Marking scheme: Truth table, k-map, logic expression, design

b) Draw ASM chart for a 2 bit up counter with output 'Q1Q0' and Enable signal X is to be designed. If X=0, counter changes the state as '00-01-10-11'. If X=1, counter should remain in present state.

[4 marks]

*Marking scheme:* State diagram, ASM chart, state table, logic expression/function, circuit diagram.

c) Explain the basic architecture of CPLD with suitable diagram. [4 marks]

Marking scheme: Architecture and explanation.