G.R. No.

Paper Code - U 239-134 (ESE)

## DECEMBER 2019 ENDSEM S. Y. B.TECH. (E & TC) (SEMESTER -III)

COURSE NAME: Electronics Devices & Circuits

COURSE CODE: ETUA21184 (PATTERN 2018) [Max. Marks: 50] Time: [2 Hours] (\*) Instructions to candidates: All questions are compulsory. 1) Figures to the right indicate full marks. 2) Use of scientific calculator is allowed. Assume suitable data where ever required. 4) Q.1)Attempt any one a) Compare Full wave and half wave rectifier with neat diagrams of [4] both and other parameters. b) Explain working principle of LED and state its applications. [4] Attempt any one Voltage divider biasing circuit uses silicon BJT has  $\beta$  = 150, Vcc = 5 [4] V,  $R_1$  = 9 K $\Omega$ ,  $R_2$  = 2.25 K $\Omega$ ,  $R_E$  = 200  $\Omega$  and  $R_c$  = 1 K $\Omega$ . Find  $I_{BQ}$ , and b) Draw and explain hybrid model of BJT for common emitter 4 configuration. Attempt any one The self-bias circuit using n-channel JFET has  $V_{DD} = 18 \text{ V}$ ,  $R_D = 4.7$ [6]  $K\Omega$ ,  $R_S = 1.5 K\Omega$  and  $R_G = 1M\Omega$ . Determine the co-ordinates of Q point such as IDQ, VGSQ and VDSQ. Assume JFET has VP = -4V, IDSS = 8 mA and  $g_m = 5$  mS. b) CS amplifier using n-channel JFET with self-bias and unbypassed [6] source resistor has R<sub>G</sub> = 1.5 M $\Omega$ , R<sub>D</sub> = 3 K $\Omega$ , R<sub>S</sub> = 1.2 K $\Omega$ , and V<sub>DD</sub> = 20 V. The JFET parameters are  $I_{DSS}$  = 8 mA,  $V_P$  = -8 V and  $Y_{OS}$  = 20  $\mu$ S, V<sub>GSQ</sub> = - 2 V, I<sub>DQ</sub> = 2 mA. Calculate g<sub>m</sub>, r<sub>0</sub> and Av. Q.4)Attempt any one a) Voltage divider biasing circuit using n-channel E-MOSFET has VDD = 5V,  $R_1$  = 30 K $\Omega$ ,  $R_2$  = 20 K $\Omega$ ,  $R_D$  = 20K $\Omega$ ,  $V_T$  = 1V,  $K_n$  = 0.1 mA/ $v^2$ . Determine the co-ordinates of Q point such as VDSQ, VGSQ and IDQ.

Explain following non-ideal effects for MOSFET.

- i) Break down effect

- ii) Channel length modulation.

- b) Draw the constructional (structure) diagram of n-channel E-MOSFET and explain its working with the help of both [6+4] characteristics.

An NMOS transistor is fabricated in a 0.4-um process having  $\mu$ mCox = 200  $\mu$ A/V2 and VA = 40 V. If L = 0.8  $\mu$ m and W = 16  $\mu$ m. Find  $\lambda$  and ID that results when the device is operated with an overdrive voltage (VGS - VT) = 0.5 V and VDS = 1 V.

## Attempt any one Q.5)

a) Common source amplifier using n-channel E-MOSFET has  $R_1 = 40 [7+6]$  $M\Omega$ ,  $R_2 = 10 M\Omega$ ,  $R_D = 4.7 K\Omega$ ,  $R_{sig}$  or  $R_{source} = 2.2 K\Omega$  and  $V_{DD} = 25$ V. If MOSFET parameters are  $V_T = 3 \text{ V}$ ,  $K_n = 0.4 \text{ mA/V}^2$  and ro = 40 KΩ. Calculate Av, Ri and Ro.

Draw voltage divider biasing common source amplifier circuit using n-channel E-MOSFET and write the expressions for AV, Ri and Ro.

b) Determine IDO, gm and ro for a MOSFET CS amplifier if VDD = 5V, [7+6]  $V_{GSQ} = 2.12V$ ,  $R_D = 2.5K\Omega$ . Assume transistor parameters as  $V_T = 1V$ ,  $K_n = 0.8 \text{ mA/V}^2 \text{ and } \lambda = 0.02/V.$

Draw and explain the high frequency AC equivalent circuit for n channel E-MOSFET and explain the effect of source terminal resistances, Rs on the gain of the CS amplifier.

## Q.6) Attempt any one

a) Explain working of Hartley oscillator with neat circuit diagram. [7] A Hartley Oscillator circuit has two inductances of L1=L2 =100 µH and  $C = 0.05\mu F$ . Determine the frequency of oscillations of the circuit.

Draw block schematic of following feedback topologies:

- i) Voltage shunt feedback topology

- ii) Current shunt feedback topology

- iii) Current series feedback topology

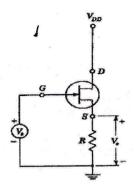

- b) For the FET source follower circuit, calculate values of Avf, Rif, Rof [7+6] and R'of. Assume  $g_m = 2 \text{ mA/V}$  and  $r_d = 40 \text{ K}\Omega$  and  $R = 3 \text{K}\Omega$ .

Draw the block diagram of voltage series negative feedback amplifier and derive the expression for Avf.